verilog实现串口功能

预览截图

应用介绍

内核的主要代码位于rtl子目录中。 uart_rx.v和uart_tx.v文件是实际的实现,uart.v只是实例化这两个模块并建立了两个内部连接。

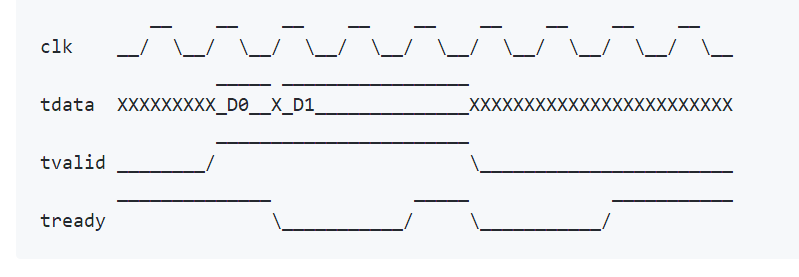

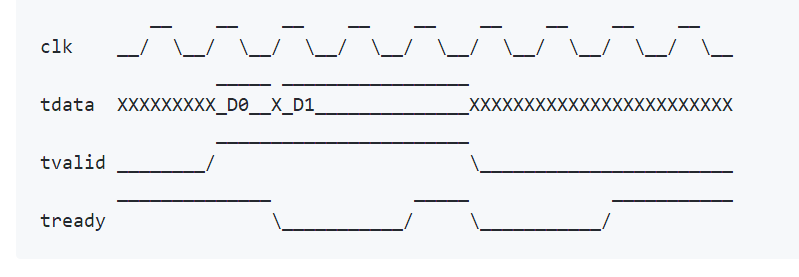

UART发送器和接收器均使用单个发送或接收引脚。这些模块采用一个参数DATA_WIDTH,该参数指定数据总线的宽度和通信的实际数据字的长度。 8位接口的默认值为8。预分频输入决定数据速率-应将其设置为Fclk /(波特* 8)。尽管它不是内部缓冲的,但它是输入而不是参数,因此可以在运行时更改它,因此应小心避免损坏数据。用户设计的主要接口是AXI4-Stream接口,由tdata,tvalid和tready信号组成。当tvalid为高时,tdata被视为有效。仅当tready信号为高时,目的地才会接受数据。仅当tvalid和tready都很高时,数据才从源传输到目标,否则总线将停止。

当进行操作时,两个接口都呈现高电平的“忙”信号。接收器还显示溢出错误和帧错误选通输出。如果在接收另一个字之前未读取当前tdata输出寄存器中的数据字,则将从overrun_error发出单个周期脉冲,并丢弃该字。如果接收器未获得正确电平的停止位,则将从frame_error输出中发出单个脉冲,并丢弃接收到的字。

©版权声明:本文内容由互联网用户自发贡献,版权归原创作者所有,本站不拥有所有权,也不承担相关法律责任。如果您发现本站中有涉嫌抄袭的内容,欢迎发送邮件至: [email protected] 进行举报,并提供相关证据,一经查实,本站将立刻删除涉嫌侵权内容。

转载请注明出处: apollocode » verilog实现串口功能

文件列表(部分)

| 名称 | 大小 | 修改日期 |

|---|---|---|

| vivado.mk | 1.19 KB | 2019-04-04 |

| Makefile | 0.40 KB | 2019-04-04 |

| fpga.xdc | 0.70 KB | 2019-04-04 |

| uart | 0.01 KB | 2019-04-04 |

| Makefile | 0.24 KB | 2019-04-04 |

| debounce_switch.v | 1.14 KB | 2019-04-04 |

| fpga.v | 1.69 KB | 2019-04-04 |

| fpga_core.v | 1.48 KB | 2019-04-04 |

| sync_reset.v | 0.93 KB | 2019-04-04 |

| sync_signal.v | 0.98 KB | 2019-04-04 |

| xilinx.mk | 2.23 KB | 2019-04-04 |

| Makefile | 0.42 KB | 2019-04-04 |

| fpga.ucf | 2.63 KB | 2019-04-04 |

| uart | 0.01 KB | 2019-04-04 |

| Makefile | 0.24 KB | 2019-04-04 |

| debounce_switch.v | 1.14 KB | 2019-04-04 |

| fpga.v | 1.66 KB | 2019-04-04 |

| fpga_core.v | 1.48 KB | 2019-04-04 |

| sync_reset.v | 0.93 KB | 2019-04-04 |

| sync_signal.v | 0.98 KB | 2019-04-04 |

| xilinx.mk | 2.23 KB | 2019-04-04 |

| Makefile | 0.46 KB | 2019-04-04 |

| fpga.ucf | 1.23 KB | 2019-04-04 |

| uart | 0.01 KB | 2019-04-04 |

| Makefile | 0.24 KB | 2019-04-04 |

| debounce_switch.v | 1.14 KB | 2019-04-04 |

| fpga.v | 1.96 KB | 2019-04-04 |

| fpga_core.v | 1.54 KB | 2019-04-04 |

| sync_reset.v | 0.93 KB | 2019-04-04 |

| sync_signal.v | 0.98 KB | 2019-04-04 |

发表评论 取消回复