[FPGA教程] Basys 3 FPGA上的七段LED显示

应用介绍

此项目是[FPGA教程] Basys 3 FPGA上的七段LED显示。

该FPGA教程将指导您如何控制Basys 3 FPGA板上的4位七段显示器。 将在Verilog中设计一个显示控制器,以在Basys 3 FPGA的4位7段LED显示屏上显示数字。 还将提供七段式LED显示控制器的完整Verilog代码。

Basys 3 FPGA具有一个共阳极4位7段LED显示屏,如下图所示。

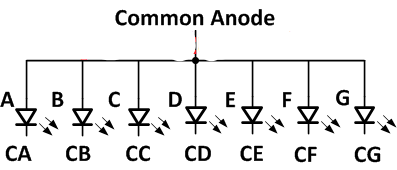

单个LED的七个段中的七个阳极连接到一个公共阳极节点,而其阴极则分开,如下图所示。

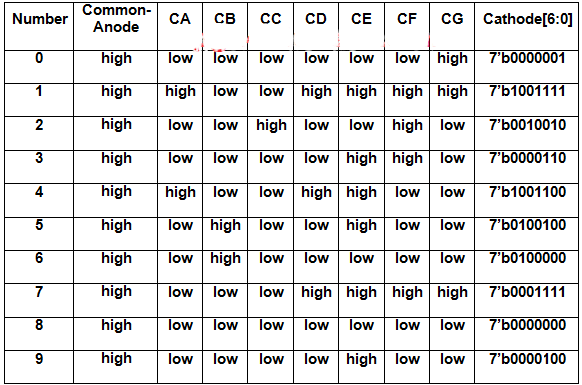

为了照亮诸如A-G之类的LED段,这些段的阳极需要处于“高”逻辑电平,而阴极应处于“低”逻辑电平。 因此,公共阳极节点应较高以激活单个七段LED显示器。 阴极的逻辑电平可以从低(发光)到高(未发光)变化,以在单个7段LED显示屏上显示不同的十进制值,如下所示。

如上图所示,我们可以通过打开和关闭单个七段式LED显示屏的七个段,在七段式LED显示屏上显示从零到九的数字。 例如,要在LED上显示数字“ 1”,段A,F,G,E和D不亮,或者它们的阴极应该高,而B-C段要亮,或者它们的阴极应该低。 同样,我们可以获得以下解码器表,用于在七段LED显示屏上显示十个数字:

该表显示了所需的阴极图形,用于在Basys 3 FPGA板的单个7段LED显示屏上显示相应的数字。

目前,我们知道如何在Basys 3 FPGA板上的单个七段LED显示屏上显示数字。 但是,Basys 3上的四个七段LED的阴极不是分开的,而是连接在一起,如下图所示。

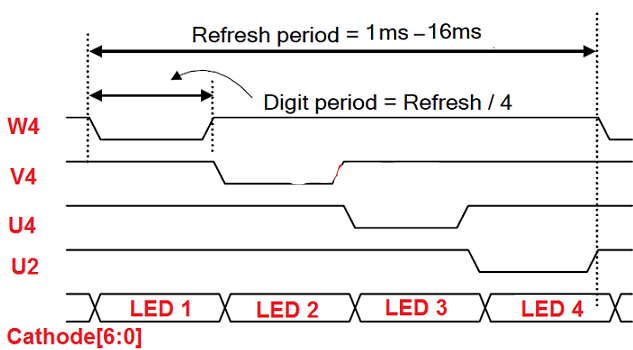

因此,要在4位七段LED显示器上显示4个不同的数字,我们必须通过在不同时间激活四个七段LED来分别控制四个七段LED的阴极(CA-CG)。 例如,当我们通过将A1驱动为高电平来激活LED 1,而其他三个LED(LED 2,LED 3,LED 4)被停用(未驱动A2,A3和A4)时,阴极图案(CA-CG)将变为 用于在LED 1上显示数字。类似地,LED 2-LED 4可以在不同的时间使用相同的方式显示。 如上图所示,我们可以使用4个PNP晶体管AN0-AN3来控制激活四个7段LED。 当晶体管导通或基极端子(W4,U4,V4或U2)为低电平时,相应的阳极被驱动为高电平,以激活或启用相应的七段式LED。

点亮后禁用LED时,它会变暗。 为避免人眼感知到的显示不连续性,四个七段式LED应以大约1KHz至60Hz的频率连续刷新,或者应每1ms至16ms的频率刷新一次。

在该项目中,设计了一个7段LED显示控制器,用于在Basys 3 FPGA板的4位7段LED显示屏上显示数字。 以下是Basys 3 FPGA上的七段LED显示控制器的时序图:

下面是一个示例时序图,用于在Basys 3 FPGA板的4位7段LED显示屏上以60Hz的刷新率或16ms的周期显示“ 1234”:

Basys 3 FPGA的时钟源为100MHz,我们需要1ms-16ms的刷新周期或1KHz-60Hz的刷新率。 我将选择10.5ms的刷新周期(数字周期= 2.6ms),以便我们可以使用20位计数器创建刷新周期,而计数器的前2个MSB位用于创建LED激活信号(数字周期为 2.6ms),如上面的时序图所示。

本人在下方展示了用于创建刷新信号和LED激活信号的示例Verilog代码:如想了解的更多请下载附件。

reg [19:0] refresh_counter;

// the first 18-bit for creating 2.6ms digit period

// the other 2-bit for creating 4 LED-activating signals

wire [1:0] LED_activating_counter;

// count 0 -> 1 -> 2 -> 3

// activates LED1 LED2 LED3 LED4

// and repeat

always @(posedge clock_100Mhz or posedge reset)

begin

if(reset==1)

refresh_counter <= 0;

else

refresh_counter <= refresh_counter + 1;

end

assign LED_activating_counter = refresh_counter[19:18];

©版权声明:本文内容由互联网用户自发贡献,版权归原创作者所有,本站不拥有所有权,也不承担相关法律责任。如果您发现本站中有涉嫌抄袭的内容,欢迎发送邮件至: [email protected] 进行举报,并提供相关证据,一经查实,本站将立刻删除涉嫌侵权内容。

转载请注明出处: apollocode » [FPGA教程] Basys 3 FPGA上的七段LED显示

文件列表(部分)

| 名称 | 大小 | 修改日期 |

|---|---|---|

| [FPGA教程] Basys 3 FPGA上的七段LED显示(附件).txt | 1.73 KB | 2020-04-08 |

| 7_segment_LED_FPGA_Tutorial.png | 7.83 KB | 2020-04-08 |

| FPGA_tutorial_7segment_LED_Basys3.png | 49.72 KB | 2020-04-08 |

| FPGA_Tutorial_7_segment_LED.png | 501.40 KB | 2020-04-08 |

| Seven_segment_Display_FPGA_tutorial.png | 67.13 KB | 2020-04-08 |

| Seven_segment_display_table.png | 15.36 KB | 2020-04-08 |

| Seven_segment_LED_display_Basys3.png | 82.67 KB | 2020-04-08 |

| Timing_diagram_seven_segmend_LED.png | 42.34 KB | 2020-04-08 |

| image | 0.00 KB | 2020-04-08 |

发表评论 取消回复