选择器的Verilog代码

此项目是选择器的Verilog代码。多路选择器是数字电路中主要的组合逻辑组件之一。 多路选择器用于选择许多不同的数字输入之一,并根据控制信号转发到输出。在此Verilog项目中,介绍了用于多路复用器(例如2对1多路选择器,2x5至5多路选择器和2x32至32多路选择器)的Verilog代码。了解更多请下载附件。

应用介绍

此项目是选择器的Verilog代码。

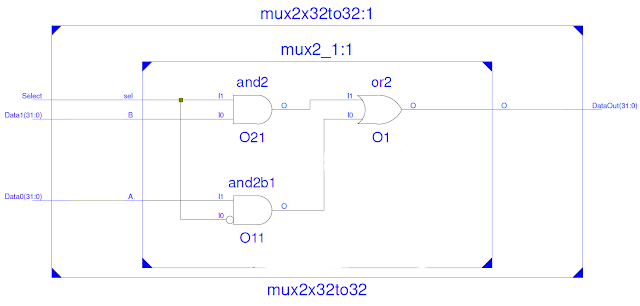

多路选择器是数字电路中主要的组合逻辑组件之一。 多路选择器用于选择许多不同的数字输入之一,并根据控制信号转发到输出。在此Verilog项目中,介绍了用于多路复用器(例如2对1多路选择器,2x5至5多路选择器和2x32至32多路选择器)的Verilog代码。

本人在下方展示了一小部分复用器的Verilog代码;如想了解更多请下载附件。

// fpga4student.com: FPGA projects, Verilog projects, VHDL projects

// Verilog project: Verilog code for Multiplexer

// Verilog code for 2x32-to-32 Multiplexer

module mux2x32to32( DataOut,Data0, Data1, Select);

output [31:0] DataOut; // Data Out

input [31:0] Data0, Data1; // Data In 1 and 2

input Select;

// if Select = 0, DataOut = Data0

// otherwise, DataOut = Data1

mux2_1 mux0(DataOut[0],Data0[0],Data1[0],Select);

mux2_1 mux1(DataOut[1],Data0[1],Data1[1],Select);

mux2_1 mux2(DataOut[2],Data0[2],Data1[2],Select);

mux2_1 mux3(DataOut[3],Data0[3],Data1[3],Select);

mux2_1 mux4(DataOut[4],Data0[4],Data1[4],Select);

mux2_1 mux5(DataOut[5],Data0[5],Data1[5],Select);

mux2_1 mux6(DataOut[6],Data0[6],Data1[6],Select);

mux2_1 mux7(DataOut[7],Data0[7],Data1[7],Select);

mux2_1 mux8(DataOut[8],Data0[8],Data1[8],Select);

mux2_1 mux9(DataOut[9],Data0[9],Data1[9],Select);

mux2_1 mux10(DataOut[10],Data0[10],Data1[10],Select);

mux2_1 mux11(DataOut[11],Data0[11],Data1[11],Select);

mux2_1 mux12(DataOut[12],Data0[12],Data1[12],Select);

mux2_1 mux13(DataOut[13],Data0[13],Data1[13],Select);

©版权声明:本文内容由互联网用户自发贡献,版权归原创作者所有,本站不拥有所有权,也不承担相关法律责任。如果您发现本站中有涉嫌抄袭的内容,欢迎发送邮件至: [email protected] 进行举报,并提供相关证据,一经查实,本站将立刻删除涉嫌侵权内容。

转载请注明出处: apollocode » 选择器的Verilog代码

文件列表(部分)

| 名称 | 大小 | 修改日期 |

|---|---|---|

| 复用器的Verilog代码(附件).txt | 0.69 KB | 2020-04-05 |

| m1.png | 17.29 KB | 2020-04-05 |

| image | 0.00 KB | 2020-04-05 |

发表评论 取消回复