算术逻辑单元(ALU)的Verilog代码

此项目是算术逻辑单元(ALU)的Verilog代码。上一次,在VHDL中设计并实现了算术逻辑单元(ALU)。 提出了用于ALU的完整VHDL代码。现在,apollocode提供了ALU的Verilog代码。 还提供了用于ALU的testbench Verilog代码以进行仿真。附件中包括:ALU的Verilog代码、ALU的Testbench Verilog代码、ALU的仿真波形。了解更多请下载附件。

应用介绍

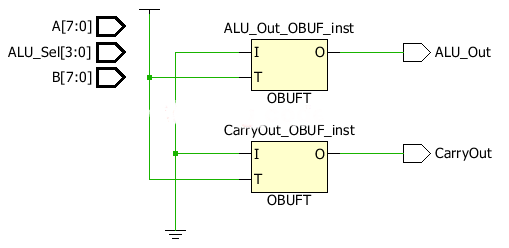

此项目是算术逻辑单元(ALU)的Verilog代码。

上一次,在VHDL中设计并实现了算术逻辑单元(ALU)。 提出了用于ALU的完整VHDL代码。现在,apollocode提供了ALU的Verilog代码。 还提供了用于ALU的testbench Verilog代码以进行仿真。

附件中包括:ALU的Verilog代码、ALU的Testbench Verilog代码、ALU的仿真波形。

本人在下方展示了ALU的Testbench Verilog代码;想了解更多请下载附件。

// fpga4student.com: FPGA projects, Verilog projects, VHDL projects

// Verilog project: Verilog code for ALU

// by FPGA4STUDENT

`timescale 1ns / 1ps

module tb_alu;

//Inputs

reg[7:0] A,B;

reg[3:0] ALU_Sel;

//Outputs

wire[7:0] ALU_Out;

wire CarryOut;

// Verilog code for ALU

integer i;

alu test_unit(

A,B, // ALU 8-bit Inputs

ALU_Sel,// ALU Selection

ALU_Out, // ALU 8-bit Output

CarryOut // Carry Out Flag

);

initial begin

// hold reset state for 100 ns.

A = 8'h0A;

B = 4'h02;

ALU_Sel = 4'h0;

for (i=0;i<=15;i=i+1)

begin

ALU_Sel = ALU_Sel + 8'h01;

#10;

end;

A = 8'hF6;

B = 8'h0A;

end

endmodule

©版权声明:本文内容由互联网用户自发贡献,版权归原创作者所有,本站不拥有所有权,也不承担相关法律责任。如果您发现本站中有涉嫌抄袭的内容,欢迎发送邮件至: [email protected] 进行举报,并提供相关证据,一经查实,本站将立刻删除涉嫌侵权内容。

转载请注明出处: apollocode » 算术逻辑单元(ALU)的Verilog代码

文件列表(部分)

| 名称 | 大小 | 修改日期 |

|---|---|---|

| 算术逻辑单元(ALU)的Verilog代码 (附件).txt | 1.00 KB | 2020-04-05 |

| alu1.png | 20.34 KB | 2020-04-05 |

| alu2.png | 12.23 KB | 2020-04-05 |

| image | 0.00 KB | 2020-04-05 |

发表评论 取消回复